Home / Technology / Chip Packaging Bottleneck Looms for AI

Chip Packaging Bottleneck Looms for AI

8 Apr

Summary

- Advanced chip packaging, crucial for AI, is concentrated in Asia.

- TSMC and Intel are expanding U.S. packaging capacity.

- Nvidia has reserved most of TSMC's advanced packaging capacity.

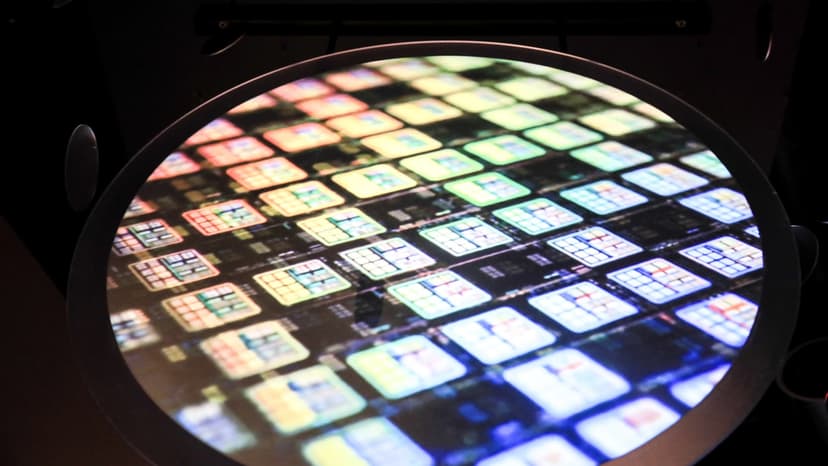

A crucial yet often overlooked step in chip manufacturing, advanced packaging, is emerging as a potential bottleneck for the burgeoning artificial intelligence industry. Currently, the vast majority of this essential process occurs in Asia, leading to a global shortage of capacity.

Taiwan Semiconductor Manufacturing Co. (TSMC) is preparing to significantly expand its U.S. presence with new plants in Arizona. Concurrently, Intel is bolstering its custom chip plans, leveraging its advanced packaging technology. Experts warn that a lack of proactive capital investment could exacerbate this bottleneck as fab output surges in the coming years.

TSMC's North America packaging solutions head confirmed substantial growth, with their Chip on Wafer on Substrate (CoWoS) method growing at an 80% compound annual growth rate. AI powerhouse Nvidia has already reserved the majority of the most advanced packaging capacity available at TSMC. Intel, though still seeking major external fabrication clients, boasts customers like Amazon and Cisco for its packaging services, positioning itself as a key player in the U.S. market.